# Analog Monitor and Control Circuit with 10-Bit, Multi-Channel ADC and Four DACs, Temperature Sensor, and 12 GPIOs

Check for Samples: AMC7891

#### **FEATURES**

- 10-Bit, 500-kSPS SAR ADC:

- 8 External Analog Inputs

- V<sub>REF</sub>, 2 × V<sub>REF</sub> Input Ranges

- Four 10-Bit Monotonic DACs:

- 0 to 5-V Output Range

- Up to 10-mA Sink and Source Capability

- Power-On Reset to 0 V

- Internal 2.5-V Reference

- Internal Temperature Sensor:

- 40°C to +125°C Operation

- Accuracy of ±2.5°C

- 12 General-Purpose I/O Ports:

- 1.8-V to 5.5-V Operation

- Low-Power SPI™-Compatible Serial Interface:

- 4-Wire Mode, 1.8-V to 5.5-V Operation

- SCLK up to 30 MHz

- Temperature Range: –40°C to +105°C

- Low Power: 32.5 mW at 5 V, Full Operating Conditions

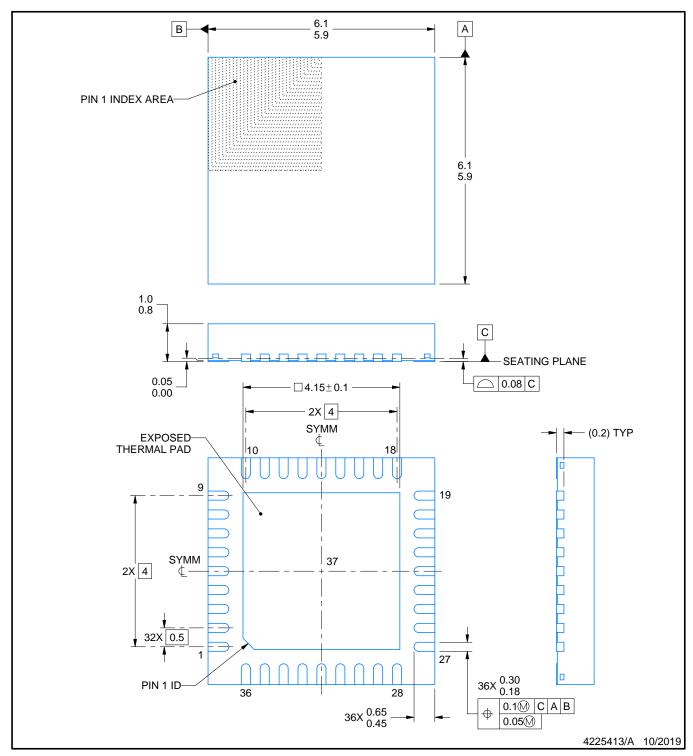

- Space-Saving Package: 36-pin, 6-mm x 6-mm QFN

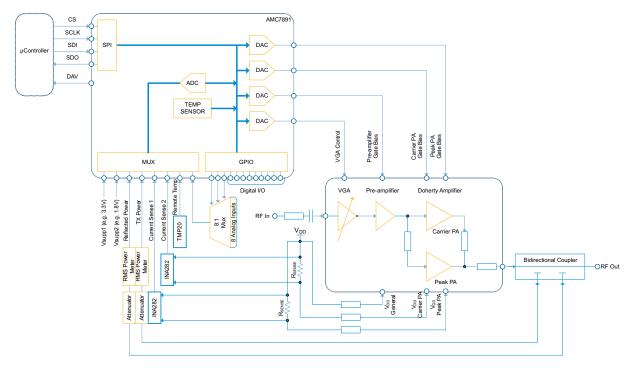

#### APPLICATIONS

- · Cellular Base Stations

- RF Communication Systems

- Optical Networks

- General-Purpose Monitor and Control

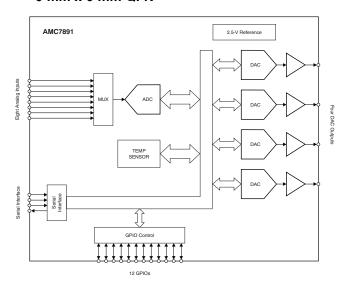

#### DESCRIPTION

The AMC7891 is a highly-integrated, low-power, complete analog monitoring and control system in a very small package.

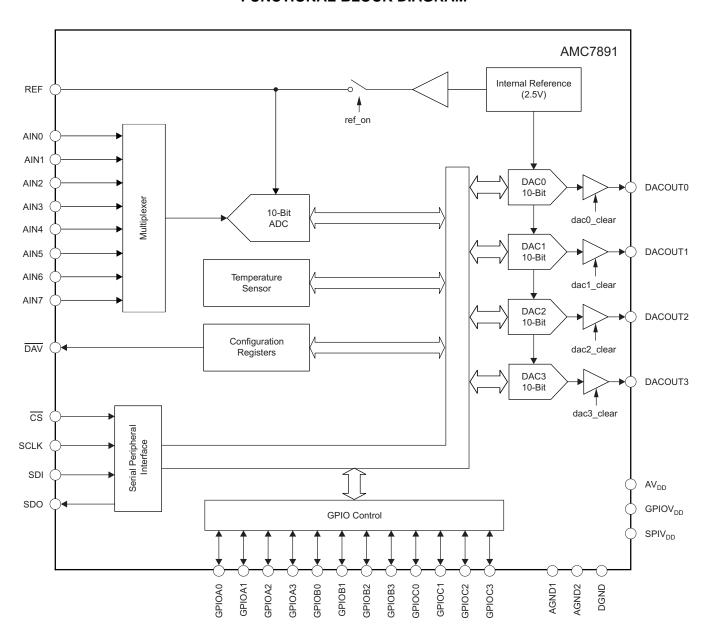

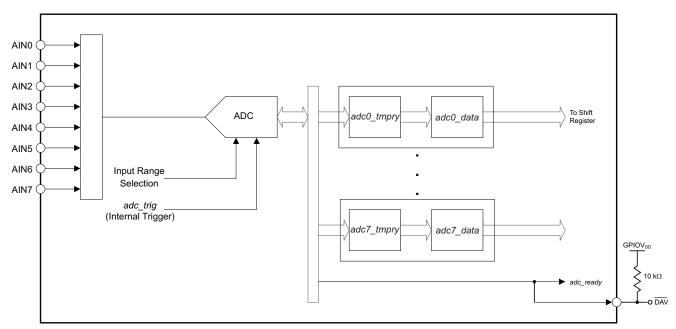

For monitoring functions, the AMC7891 has 8 uncommitted inputs multiplexed into a 10-bit SAR analog-to-digital converter (ADC) and an accurate on-chip temperature sensor. Control signals are generated through four, independent, 10-bit digital-to-analog converters (DACs). Additional digital signal monitoring and control is accomplished through twelve configurable GPIOs. An internal reference can be used to drive the ADC and DACs.

Communication to the device is performed through a versatile, four-wire serial interface compatible with industry-standard microprocessors and microcontrollers. The serial interface can operate at clock rates up to 30 MHz, allowing quick access to critical system data.

The device is characterized for operation over the temperature range of -40°C to 105°C and is available in a very small, 36-pin, 6-mm x 6-mm QFN package.

The AMC7891's low power, small size and high-integration make it an ideal low-cost, bias control circuit for modern RF transistor modules such as the power amplifiers (PA) and low-noise amplifiers (LNA) found in RF communication systems. The AMC7891 feature set is similarly beneficial in general purpose monitor and control systems.

For applications that require a different channel count, additional features, or converter resolutions, Texas Instruments offers a complete family of Analog Monitor and Control (AMC) Products. See http://www.ti.com/amc.

M

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SPI is a trademark of Motorola, Inc.

All other trademarks are the property of their respective owners.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

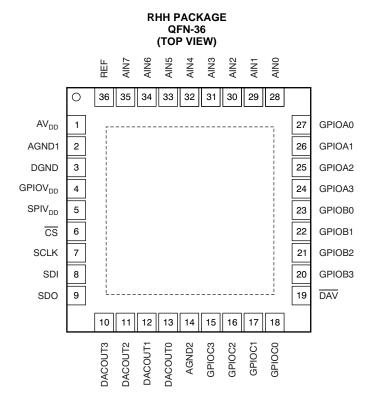

#### **AMC7891 Pin Functions**

| PIN I/O |                     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |

|---------|---------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO.     | NAME                | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                             |

| 1       | AV <sub>DD</sub>    | I   | Analog supply voltage. (4.75 V to 5.5 V)                                                                                                                                                                                                                                                                                                                |

| 2       | AGND1               | I   | Analog ground. Ground reference point for all analog circuitry on the device, AGND. Connect AGND1 and AGND2 to the same potential, AGND.                                                                                                                                                                                                                |

| 3       | DGND                | I   | Digital ground. Ground reference point for all digital circuitry on the device. Ideally, AGND and DGND should be at the same potential and must not differ by more than 0.3 V.                                                                                                                                                                          |

| 4       | GPIOV <sub>DD</sub> | I   | GPIO supply voltage. (1.8 V to 5.5 V) Sets the GPIO operating voltage and threshold levels.                                                                                                                                                                                                                                                             |

| 5       | SPIV <sub>DD</sub>  | I   | Serial interface supply voltage. (1.8 V to 5.5 V) Sets the serial interface operating voltage and threshold levels.                                                                                                                                                                                                                                     |

| 6       | CS                  | I   | Active low serial data enable. Schmitt-trigger logic input.                                                                                                                                                                                                                                                                                             |

|         |                     |     | This input is the frame synchronization signal for the serial data. When this signal goes low, it enables the input shift register and data is sampled on subsequent falling clock edges. The DAC output and register settings update following the 24th clock. If $\overline{\text{CS}}$ goes high before the 23th clock edge, the command is ignored. |

| 7       | SCLK                | I   | Serial interface clock. Schmitt-trigger logic input.  Maximum SCLK rate is 30MHz.                                                                                                                                                                                                                                                                       |

| 8       | SDI                 | I   | Serial interface data input. Schmitt-trigger logic input. Data is clocked into the input shift register on each falling edge of SCLK.                                                                                                                                                                                                                   |

| 9       | SDO                 | 0   | Serial interface data output. The SDO pin is in high impedance when $\overline{\text{CS}}$ is high. Data is clocked out of the input shift register on each rising edge of SCLK.                                                                                                                                                                        |

| 10      | DACOUT3             | 0   | DAC3 buffered output. (0 V to AV <sub>DD</sub> ).<br>Can source/sink up to 10 mA.                                                                                                                                                                                                                                                                       |

# **AMC7891 Pin Functions (continued)**

|     | PIN            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|----------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME           | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 11  | DACOUT2        | 0   | DAC2 buffered output. (0 V to AV <sub>DD</sub> ). Can source/sink up to 10 mA.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 12  | DACOUT1        | 0   | DAC1 buffered output. (0 V to AV <sub>DD</sub> ). Can source/sink up to 10 mA.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13  | DACOUT0        | 0   | DAC0 buffered output. (0 V to AV <sub>DD</sub> ). Can source/sink up to 10 mA.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 14  | AGND2          | I   | Analog ground. Ground reference point for all analog circuitry on the device, AGND. Connect AGND1 and AGND2 to the same potential, AGND.                                                                                                                                                                                                                                                                                                                                           |

| 15  | GPIOC3         | I/O | General purpose digital I/O C3. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 16  | GPIOC2         | I/O | General purpose digital I/O C2. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 17  | GPIOC1         | I/O | General purpose digital I/O C1. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 18  | GPIOC0         | I/O | General purpose digital I/O C0. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 19  | DAV            | 0   | ADC data available indicator. Open-drain, active low output.                                                                                                                                                                                                                                                                                                                                                                                                                       |

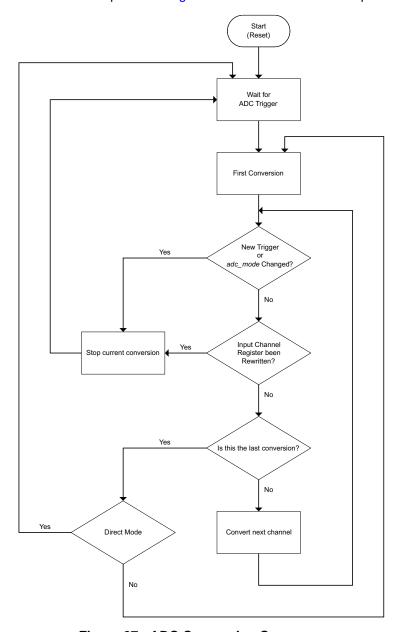

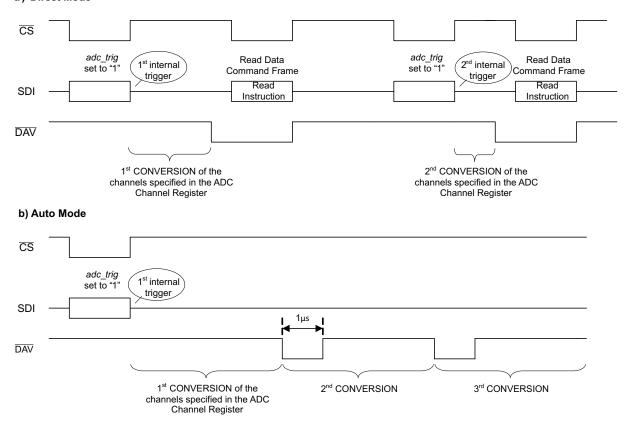

|     |                |     | In direct-mode, $\overline{DAV}$ goes low when an ADC conversion cycle finishes. In auto-mode a 1µs pulse appears on this pin when the conversion cycle finishes (see ADC Operation for details). $\overline{DAV}$ stays high when deactivated. If used, an external 10 k $\Omega$ pull-up resistor to GPIOV <sub>DD</sub> is required. If unused, the pin can be connected to DGND.                                                                                               |

| 20  | GPIOB3         | I/O | General purpose digital I/O B3. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 21  | GPIOB2         | I/O | General purpose digital I/O B2. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 22  | GPIOB1         | I/O | General purpose digital I/O B1. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 23  | GPIOB0         | I/O | General purpose digital I/O B1. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 24  | GPIOA3         | I/O | General purpose digital I/O A3. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 25  | GPIOA2         | I/O | General purpose digital I/O A2. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26  | GPIOA1         | I/O | General purpose digital I/O A1. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 27  | GPIOA0         | I/O | General purpose digital I/O A1. Maximum voltage is set by GPIOV <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                      |

| 28  | AIN0           | ı   | Uncommitted analog input 0. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 29  | AIN1           | ı   | Uncommitted analog input 1. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 30  | AIN2           | I   | Uncommitted analog input 2. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 31  | AIN3           | I   | Uncommitted analog input 3. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 32  | AIN4           | I   | Uncommitted analog input 4. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 33  | AIN5           | ı   | Uncommitted analog input 5. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 34  | AIN6           | ı   | Uncommitted analog input 6. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 35  | AIN7           | ı   | Uncommitted analog input 7. (0 V to 5 V)                                                                                                                                                                                                                                                                                                                                                                                                                                           |

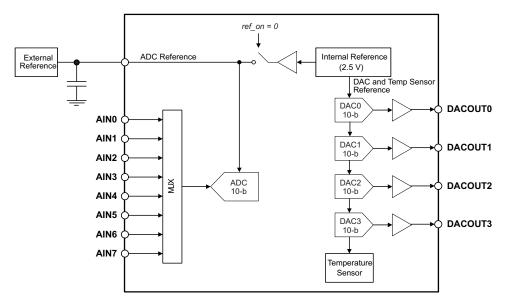

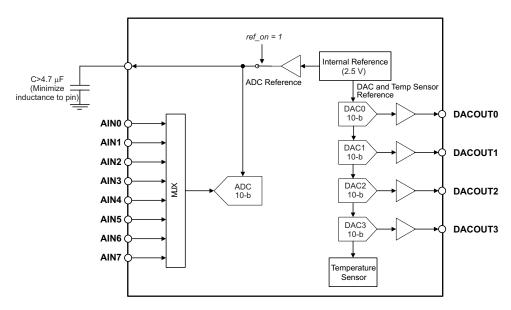

| 36  | REF            | I/O | Used as external ADC reference input when the internal reference buffer is disabled in register <i>AMC_power</i> , $ref\_on = '0'$ (default). A decoupling capacitor is recommended between the external reference output an AGND for noise filtering.  Used as internal reference output when the internal reference buffer is enabled in register <i>AMC_power</i> , $ref\_on = '1'$ . Requires a 4.7 µF decoupling capacitor to AGND when used as reference output. An external |

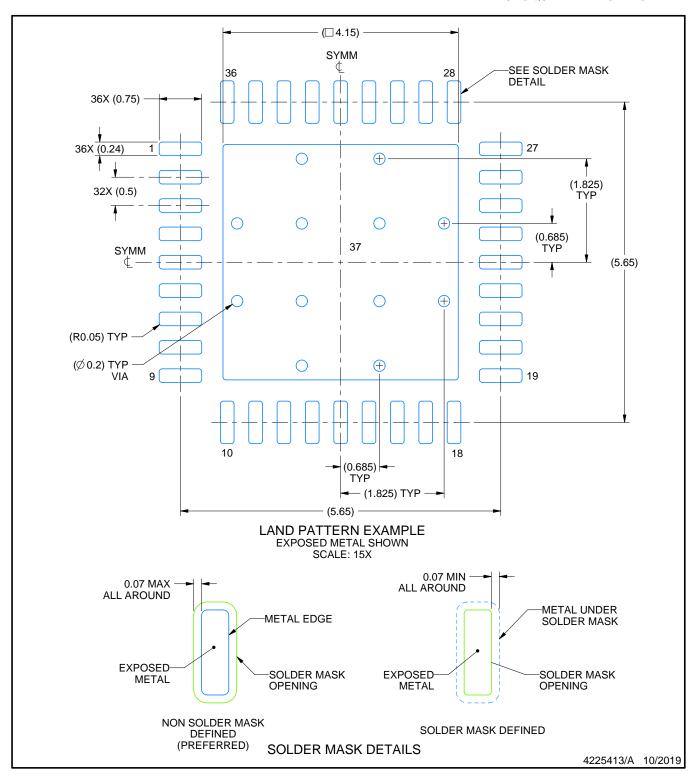

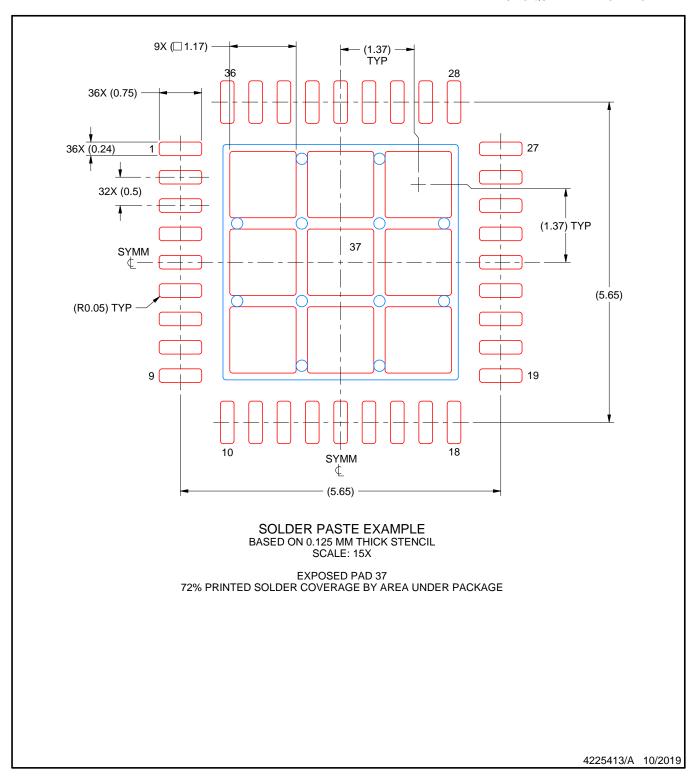

| -   | THERMAL<br>PAD | -   | buffer amplifier with high impedance input is required to drive an external load.  The thermal pad is located on the package underside. Connect to the board ground plane using multiple vias.                                                                                                                                                                                                                                                                                     |

Copyright © 2011, Texas Instruments Incorporated

## **FUNCTIONAL BLOCK DIAGRAM**

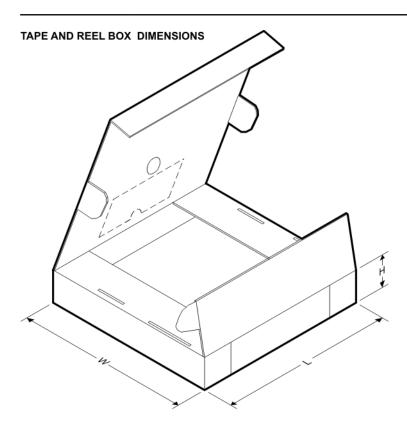

# ORDERING INFORMATION(1)

| T <sub>A</sub> | ORDER CODE   | PACKAGE<br>DRAWING/TYPE <sup>(2)(3)</sup> | TRANSPORT<br>MEDIA | QUANTITY |

|----------------|--------------|-------------------------------------------|--------------------|----------|

| 40°C to 405°C  | AMC7891SRHHT | DIJII / 26 OFN Oved Flatnack No. Load     | Tana and Daal      | 250      |

| –40°C to 105°C | AMC7891SRHHR | RHH / 36-QFN Quad Flatpack No-Lead        | Tape and Reel      | 2000     |

- (1) For the most current package and ordering information see the Package Option Addendum at the end of this document, or see the device product folder at www.ti.com.

- (2) Thermal Pad Size: 4.39 mm x 4.39 mm

- (3) MSL Peak Temperature: Level-3-260C-168 HR

# ABSOLUTE MAXIMUM RATINGS(1)

Over operating free-air temperature range, unless otherwise noted.

|                           |                                               |      | VALUE                     | UNIT |

|---------------------------|-----------------------------------------------|------|---------------------------|------|

|                           |                                               | MIN  | MAX                       |      |

| Supply voltage range      | AV <sub>DD</sub> to AGND <sup>(2)</sup>       | -0.3 | 6                         | V    |

|                           | GPIOV <sub>DD</sub> to DGND                   | -0.3 | 6                         | V    |

|                           | SPIV <sub>DD</sub> to DGND                    | -0.3 | 6                         | V    |

|                           | AGND to DGND                                  | -0.3 | 0.3                       | V    |

|                           | AIN[0:7], DACOUT[0:3], REF to AGND            | -0.3 | AV <sub>DD</sub> + 0.3    | V    |

|                           | CS, SCLK, SDI to DGND                         | -0.3 | 6                         | V    |

| Pin voltage range         | SDO to DGND                                   | -0.3 | SPIV <sub>DD</sub> + 0.3  | V    |

|                           | GPIOA[0:3], GPIOB[0:3], GPIOC[0:3] to DGND    | -0.3 | GPIOV <sub>DD</sub> + 0.3 | V    |

|                           | DAV to DGND                                   | -0.3 | 6                         | V    |

| Operating free-air temper | ature range, T <sub>A</sub> : AMC7891 (3) (4) | -40  | 105                       | °C   |

| Storage temperature rang  | je                                            | -40  | 150                       | °C   |

| ECD actions               | Human body model (HBM)                        |      | 2.5                       | kV   |

| ESD ratings:              | Charged device model (CDM)                    |      | 1.0                       | kV   |

<sup>(1)</sup> Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

|                  |                                              | AMC7891     |       |

|------------------|----------------------------------------------|-------------|-------|

|                  | THERMAL METRIC <sup>(1)</sup>                | RHH PACKAGE | UNITS |

|                  |                                              | 36 PINS     |       |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance       | 30.6        |       |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance    | 16.0        |       |

| $\theta_{JB}$    | Junction-to-board thermal resistance         | 5.3         | °C/W  |

| ΨЈТ              | Junction-to-top characterization parameter   | 0.2         | C/VV  |

| ΨЈВ              | Junction-to-board characterization parameter | 5.3         |       |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance | 0.8         |       |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

Copyright © 2011, Texas Instruments Incorporated

<sup>(2)</sup> AGND1 and AGND2 must be tied together as AGND.

<sup>(3)</sup> Air flow or heat sinking reduces  $\theta_{JA}$  and may be required for sustained operation at 105°C and maximum operating conditions.

<sup>(4)</sup> Soldering the device thermal pad to the board ground plane is strongly recommended.

# **ELECTRICAL CHARACTERISTICS (DAC SPECIFICATIONS)**

$AV_{DD}$  = 4.75 to 5.5 V,  $GPIOV_{DD}$  = 1.8 to 5.5 V,  $SPIV_{DD}$  = 1.8 to 5.5 V, AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$ ,  $T_A$  =  $-40^{\circ}C$  to 105°C (unless otherwise noted)

|      | PARAMETER                       | TEST CONDITIONS                                                                      | MIN | TYP    | MAX       | UNIT               |

|------|---------------------------------|--------------------------------------------------------------------------------------|-----|--------|-----------|--------------------|

| STAT | IC ACCURACY                     |                                                                                      |     |        |           |                    |

|      | Resolution                      |                                                                                      | 10  |        |           | Bits               |

| INL  | Relative accuracy               |                                                                                      |     | ±0.05  | ±1        | LSB                |

| DNL  | Differential nonlinearity       | Specified monotonic                                                                  |     | ±0.1   | ±1        | LSB                |

|      | Offset error                    | Code 0x008                                                                           |     | ±0.5   | ±5        | mV                 |

|      | Gain error                      |                                                                                      |     | ±0.025 | ±0.2      | %FSR               |

|      | Offset temperature coefficient  |                                                                                      |     | ±1     |           | ppm/°C             |

|      | Gain temperature coefficient    |                                                                                      |     | ±1     |           | ppm/°C             |

| DAC  | OUTPUT <sup>(1)</sup>           |                                                                                      |     |        |           |                    |

|      | Full scale output voltage range |                                                                                      | 0   |        | $AV_{DD}$ | V                  |

|      | Output voltage settling time    | Transition: Code 0x008 to 0x3F8 to within 1/2 LSB, $C_L = 2 \text{ nF}, RL = \infty$ |     | 5      |           | μs                 |

|      | Slew rate                       |                                                                                      |     | 2      |           | V/µs               |

|      | Short circuit current           | Full-scale current shorted to ground or pulled to AVDD                               |     | ±30    |           | mA                 |

|      | Load current                    | Source and/or sink within 300 mV of supply                                           |     | ±10    |           | mA                 |

|      | Capacitive load stability       | R <sub>L</sub> = ∞                                                                   | 10  |        |           | nF                 |

|      | DC output impedance             |                                                                                      |     | 1      |           | Ω                  |

|      | Power-on overshoot              | AV <sub>DD</sub> 0 to 5 V, 2 ms ramp                                                 |     | 10     |           | mV                 |

|      | Glitch energy                   | Transition: Code 0x1FF to 0x200; 0x200 to 0x1FF                                      |     | 0.15   |           | nV-s               |

|      | Output paige                    | T <sub>A</sub> = 25°C, 1 kHz                                                         |     | 260    |           | nV/√ <del>Hz</del> |

|      | Output noise                    | Integrated noise from 0.1 Hz to 10 Hz                                                |     | 20     |           | $\mu V_{PP}$       |

<sup>(1)</sup> Specified by design and characterization. Not tested during production.

# **ELECTRICAL CHARACTERISTICS – (ADC SPECIFICATIONS)**

$AV_{DD}$  = 4.75 to 5.5 V,  $GPIOV_{DD}$  = 1.8 to 5.5 V,  $SPIV_{DD}$  = 1.8 to 5.5 V, AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$ ,  $T_A$  =  $-40^{\circ}C$  to 105°C (unless otherwise noted)

|                  | PARAMETER                         | TEST CONDITIONS                                                                    | MIN        | TYP   | MAX                    | UNIT   |

|------------------|-----------------------------------|------------------------------------------------------------------------------------|------------|-------|------------------------|--------|

| DC AC            | CURACY                            |                                                                                    |            |       |                        |        |

|                  | Resolution                        |                                                                                    | 10         |       |                        | Bits   |

| INL              | Integral nonlinearity             |                                                                                    |            | ±0.1  | ±1                     | LSB    |

| DNL              | Differential nonlinearity         | Specified monotonic                                                                |            | ±0.1  | ±1                     | LSB    |

|                  | Offset error                      |                                                                                    |            | ±0.5  | ±2                     | LSB    |

|                  | Offset error match                |                                                                                    |            | ±0.4  |                        | LSB    |

|                  | Gain error                        |                                                                                    |            | ±0.5  | ±2                     | LSB    |

|                  | Gain error match                  |                                                                                    |            | ±0.4  |                        | LSB    |

| CONVE            | RSION TIME                        |                                                                                    |            |       |                        |        |

|                  | ADC conversion rate               |                                                                                    |            | 500   |                        | kSPS   |

|                  | Autocycle update rate             | All 8 ADC input channels enabled                                                   |            | 16    |                        | μs     |

|                  | Throughput rate                   | SCLK ≥ 12 MHz, single analog channel                                               |            |       | 500                    | kSPS   |

|                  | Conversion delay                  | Delay from trigger to conversion start                                             | 2          |       | 4                      | μs     |

| ANALO            | G INPUT                           |                                                                                    |            |       |                        |        |

|                  | Absolute input voltage range      | Independent of gain setting                                                        | AGND - 0.2 |       | AV <sub>DD</sub> + 0.2 | V      |

|                  | Full coals input valtage years    | Gain = 1, <i>adcn_gain</i> = '0'                                                   | 0          |       | $V_{REF}$              | V      |

|                  | Full scale input voltage range    | Gain = 2, <i>adcn_gain</i> = '1'                                                   | 0          |       | 2 × V <sub>REF</sub>   | V      |

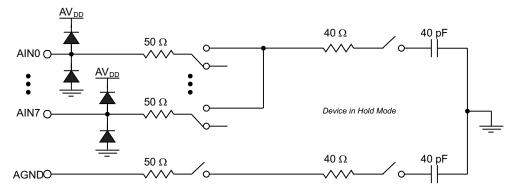

|                  | Input capacitance <sup>(1)</sup>  |                                                                                    |            | 40    |                        | pF     |

|                  | DC input leakage current          | Measured with ADC in Hold mode                                                     |            |       | ±1                     | μΑ     |

| AC PER           | RFORMANCE                         |                                                                                    |            |       |                        |        |

| SFDR             | Spurious Free Dynamic Range       | f <sub>IN</sub> = 1 kHz, -1 dBFS sine wave                                         |            | 76    |                        | dBc    |

| SNR              | Signal to Noise Ratio             | f <sub>IN</sub> = 1 kHz, -1 dBFS sine wave                                         |            | 61    |                        | dBc    |

| SINAD            | Signal to Noise+Distortion Ratio  | f <sub>IN</sub> = 1 kHz, -1 dBFS sine wave                                         |            | 60.5  |                        | dBc    |

| THD              | Total Harmonic Distortion         | f <sub>IN</sub> = 1 kHz, -1 dBFS sine wave, Measured up to the fifth harmonic      |            | 75    |                        | dBc    |

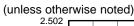

| INTERN           | NAL ADC REFERENCE (2)             |                                                                                    | -          |       |                        | !      |

| V <sub>REF</sub> | Reference output voltage          | Internal ADC reference buffered output at REF pin                                  |            | 2.5   |                        | V      |

|                  | Reference buffer power            | AV <sub>DD</sub> = 5 V                                                             |            | 360   |                        | μΑ     |

|                  | Reference temperature coefficient |                                                                                    |            | 10    |                        | ppm/°C |

| EXTER            | NAL ADC REFERENCE                 |                                                                                    |            |       |                        |        |

| $V_{REF}$        | Reference input voltage           | External ADC reference input to REF pin                                            | 0.3        |       | AVDD                   | V      |

|                  | Input resistance <sup>(1)</sup>   | V <sub>REF</sub> = 5 V, AIN = 5 V                                                  |            | 20    |                        | kΩ     |

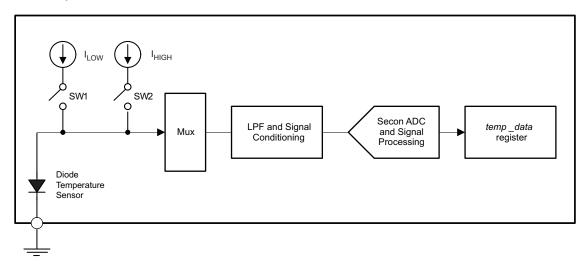

| TEMPE            | RATURE SENSOR                     |                                                                                    |            |       |                        |        |

|                  | Operating range                   |                                                                                    | -40        |       | 125                    | °C     |

|                  | Accuracy                          | $T_A = -40^{\circ}\text{C to } 125^{\circ}\text{C}, \text{ AV}_{DD} = 5 \text{ V}$ |            | ±1    | ±2.5                   | °C     |

|                  | Resolution                        | LSB size                                                                           |            | 0.125 |                        | °C     |

|                  | Conversion time                   |                                                                                    |            | 15    |                        | ms     |

Specified by design. Not tested during production. Use an external buffer amplifier with high impedance input to drive any external load.

# **ELECTRICAL CHARACTERISTICS – GENERAL SPECIFICATIONS**

$AV_{DD}$  = 4.75 to 5.5 V,  $GPIOV_{DD}$  = 1.8 to 5.5 V,  $SPIV_{DD}$  = 1.8 to 5.5 V, AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$ ,  $T_A$  =  $-40^{\circ}C$  to 105°C (unless otherwise noted)

|                 | PARAMETER                                                                         | TEST CONDITIONS                                                                         | MIN                        | TYP  | MAX | UNIT |

|-----------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------|------|-----|------|

| GENE            | RAL PURPOSE I/O                                                                   |                                                                                         |                            |      |     |      |

| .,              |                                                                                   | GPIOV <sub>DD</sub> = 1.8 V                                                             | 0.7×GPIOV <sub>DD</sub>    |      |     | V    |

| $V_{IH}$        | High-level input voltage                                                          | GPIOV <sub>DD</sub> = 3.3 to 5.5 V                                                      | 2.1                        |      |     | V    |

|                 |                                                                                   | GPIOV <sub>DD</sub> = 1.8 V                                                             |                            |      | 0.3 | V    |

| $V_{IL}$        | Low-level input voltage                                                           | GPIOV <sub>DD</sub> = 3.3 to 5.5 V                                                      |                            |      | 0.8 | V    |

| .,              |                                                                                   | I <sub>load</sub> = 1.6 mA, GPIOV <sub>DD</sub> = 1.8V, All GPIOs loaded and set to '1' | GPIOV <sub>DD</sub> - 0.25 |      |     | V    |

| V <sub>OH</sub> | High-level output voltage                                                         | $I_{load}$ = 1.6 mA, GPIOV <sub>DD</sub> = 3.3 to 5.5V, All GPIOs loaded and set to '1' | GPIOV <sub>DD</sub> - 0.2  |      |     | V    |

| V <sub>OL</sub> | Low-level output voltage                                                          | I <sub>load</sub> = -1.6 mA, All GPIOs loaded                                           |                            |      | 0.4 | V    |

|                 | Input capacitance (1)                                                             |                                                                                         |                            | 1    |     | pF   |

|                 | High impedance output capacitance (1)                                             |                                                                                         |                            | 1    |     | pF   |

| LOGIC           | NPUTS: CS, SDI, SCLK                                                              | -                                                                                       | •                          |      | ·   |      |

| .,              | LPak laval Sanatasakana                                                           | SPIV <sub>DD</sub> = 1.8 V                                                              | 0.7×SPIV <sub>DD</sub>     |      |     | V    |

| $V_{IH}$        | High-level input voltage                                                          | SPIV <sub>DD</sub> = 3.3 to 5.5 V                                                       | 2.1                        |      |     | V    |

| .,              | Laura laural importe calta da                                                     | SPIV <sub>DD</sub> = 1.8 V                                                              |                            |      | 0.3 | V    |

| $V_{IL}$        | Low-level input voltage                                                           | SPIV <sub>DD</sub> = 3.3 to 5.5 V                                                       |                            |      | 0.7 | V    |

|                 | Input current                                                                     |                                                                                         |                            |      | ±1  | μΑ   |

|                 | Input capacitance (1)                                                             |                                                                                         |                            | 1    |     | pF   |

|                 | High impedance output capacitance (1)                                             |                                                                                         |                            | 1    |     | pF   |

| LOGIC           | OUTPUT: SDO                                                                       |                                                                                         |                            |      |     |      |

| V <sub>OH</sub> | High-level output voltage                                                         | I <sub>load</sub> = 1.6 mA                                                              | SPIV <sub>DD</sub> - 0.2   |      |     | V    |

| V <sub>OL</sub> | Low-level output voltage                                                          | I <sub>load</sub> = -1.6 mA                                                             |                            |      | 0.4 | V    |

| LOGIC           | OUTPUT: DAV                                                                       |                                                                                         |                            |      |     |      |

| V <sub>OL</sub> | Low-level output voltage                                                          | I <sub>load</sub> = -2 mA                                                               |                            |      | 0.4 | V    |

| POWE            | R REQUIREMENTS                                                                    |                                                                                         |                            |      |     |      |

|                 | $AV_{DD}$                                                                         |                                                                                         | 4.75                       | 5    | 5.5 | V    |

|                 | GPIOV <sub>DD</sub>                                                               |                                                                                         | 1.8                        |      | 5.5 | V    |

|                 | SPIV <sub>DD</sub>                                                                |                                                                                         | 1.8                        |      | 5.5 | ٧    |

| I <sub>DD</sub> | Total supply current, AV <sub>DD</sub> + GPIOV <sub>DD</sub> + SPIV <sub>DD</sub> | Operating mode <sup>(2)</sup>                                                           |                            | 6.5  | 10  | mA   |

|                 |                                                                                   | Power down mode                                                                         |                            | 1.25 | 2   | mA   |

|                 | Power consumption                                                                 | Operating mode <sup>(2)</sup>                                                           |                            | 32.5 | 55  | mW   |

|                 |                                                                                   | Power down mode                                                                         |                            | 6.25 | 11  | mW   |

| OPER            | ATING RANGE                                                                       |                                                                                         |                            |      |     |      |

|                 | Specified temperature range                                                       |                                                                                         | -40                        | 25   | 105 | °C   |

<sup>(1)</sup> Specified by design. Not tested in production.

<sup>(2)</sup> AV<sub>DD</sub> = GPIOV<sub>DD</sub> = SPIV<sub>DD</sub> = 5 V. No DAC load, all DACs at 0x200 code and ADC at the fastest auto conversion rate.

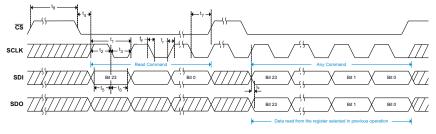

# TIMING SPECIFICATIONS(1)(2)

$AV_{DD}$  = 4.75 to 5.5 V,  $GPIOV_{DD}$  = 1.8 to 5.5 V,  $SPIV_{DD}$  = 1.8 to 5.5 V, AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$ ,  $T_A$  =  $-40^{\circ}C$  to 105°C (unless otherwise noted).

|                   | PARAMETER        | TEST CONDITIONS                                                                                  | MIN | TYP | MAX | UNIT |

|-------------------|------------------|--------------------------------------------------------------------------------------------------|-----|-----|-----|------|

|                   |                  | SPIV <sub>DD</sub> = 5.5 V                                                                       |     |     | 30  | MHz  |

| f <sub>SCLK</sub> | SCLK frequency   | SPIV <sub>DD</sub> = 2.7 V                                                                       |     |     | 15  | MHz  |

|                   |                  | SPIV <sub>DD</sub> = 1.8 V                                                                       |     |     | 10  | MHz  |

| t <sub>R</sub>    | Input rise time  | 10% to 90% of SPIV <sub>DD</sub>                                                                 |     |     | 2   | ns   |

| t <sub>F</sub>    | Input fall time  | 10% to 90% of SPIV <sub>DD</sub>                                                                 |     |     | 2   | ns   |

|                   |                  | SPIV <sub>DD</sub> = 5.5 V                                                                       | 33  |     |     | ns   |

| t <sub>1</sub>    | SCLK cycle time  | SPIV <sub>DD</sub> = 2.7 V                                                                       | 66  |     |     | ns   |

|                   |                  | SPIV <sub>DD</sub> = 1.8 V                                                                       | 100 |     |     | ns   |

|                   |                  | SPIV <sub>DD</sub> = 5.5 V                                                                       | 13  |     |     | ns   |

| $t_2$             | SCLK high time   | SPIV <sub>DD</sub> = 2.7 V                                                                       | 30  |     |     | ns   |

|                   |                  | SPIV <sub>DD</sub> = 1.8 V                                                                       | 50  |     |     | ns   |

|                   |                  | SPIV <sub>DD</sub> = 5.5 V                                                                       | 13  |     |     | ns   |

| $t_3$             | SCLK low time    | SPIV <sub>DD</sub> = 2.7 V                                                                       | 26  |     |     | ns   |

|                   |                  | SPIV <sub>DD</sub> = 1.8 V                                                                       | 40  |     |     | ns   |

| t <sub>4</sub>    | Frame start time | CS falling edge to SCLK rising edge                                                              | 5   |     |     | ns   |

| t <sub>5</sub>    | SDI setup time   | SDI valid to falling edge of SCLK                                                                | 4   |     |     | ns   |

| t <sub>6</sub>    | SDI hold time    | SDI valid after falling edge of SCLK                                                             | 12  |     |     | ns   |

| t <sub>7</sub>    | Frame stop time  | SCLK falling edge to $\overline{\text{CS}}$ rising edge                                          | 15  |     |     | ns   |

| t <sub>8</sub>    | CS high time     |                                                                                                  | 50  |     |     | ns   |

|                   |                  | $SPIV_{DD} = 5.5 \text{ V}, C_L = 10 \text{ pF}, 1 \text{ ns} \le t_{R,F(SDO)} \le 4 \text{ ns}$ | 5   |     | 16  | ns   |

| t <sub>9</sub>    | SDO delay        | $SPIV_{DD} = 2.7 \text{ V}, C_L = 10 \text{ pF}, 1 \text{ ns} \le t_{R,F(SDO)} \le 5 \text{ ns}$ | 6   |     | 22  | ns   |

|                   |                  | $SPIV_{DD} = 1.8 \text{ V}, C_L = 10 \text{ pF}, 2 \text{ ns} \le t_{R,F(SDO)} \le 8 \text{ ns}$ | 8   |     | 39  | ns   |

| t <sub>10</sub>   | Wait time        | CS rising edge to next SCLK rising edge                                                          | 5   |     |     | ns   |

- (1) Specified by design. Not tested during production.

- (2) Digital inputs and outputs timed from a voltage level of SPIV<sub>DD</sub>/2.

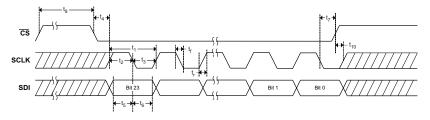

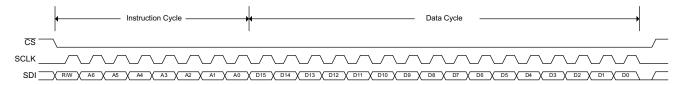

#### **TIMING INFORMATION**

Figure 1. Serial Interface Write Timing Diagram

Figure 2. Serial Interface Read Timing Diagram

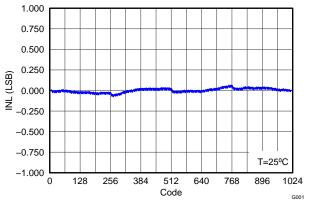

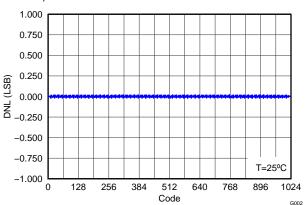

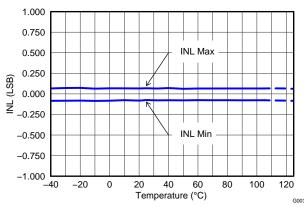

## TYPICAL CHARACTERISTICS: DAC

$AV_{DD} = 5 \text{ V}$ ,  $GPIOV_{DD} = 5 \text{ V}$ ,  $SPIV_{DD} = 5 \text{ V}$ , AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$  (unless otherwise noted)

Figure 3. DAC INTEGRAL NON-LINEARITY

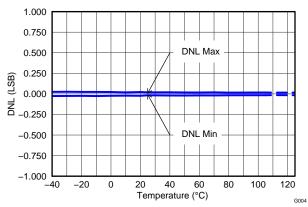

Figure 4. DAC DIFFERENTIAL NON-LINEARITY

Figure 5. DAC INL vs. TEMPERATURE

Figure 6. DAC DNL vs. TEMPERATURE

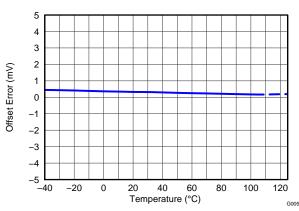

Figure 7. DAC OFFSET ERROR vs. TEMPERATURE

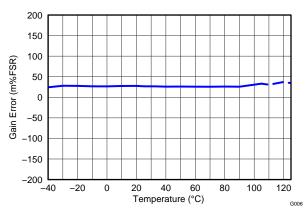

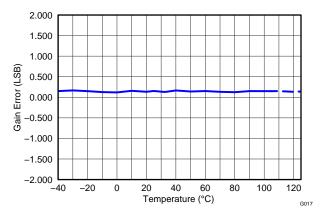

Figure 8. DAC GAIN ERROR vs. TEMPERATURE

# **TYPICAL CHARACTERISTICS: DAC (continued)**

$AV_{DD} = 5 \text{ V}$ ,  $GPIOV_{DD} = 5 \text{ V}$ ,  $SPIV_{DD} = 5 \text{ V}$ , AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$

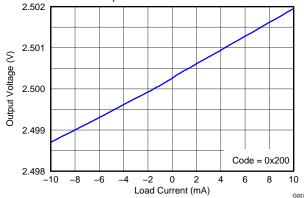

Figure 9. DAC OUTPUT VOLTAGE vs. LOAD CURRENT

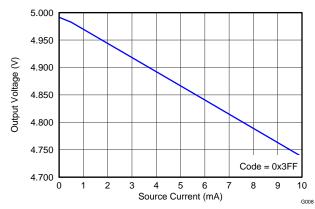

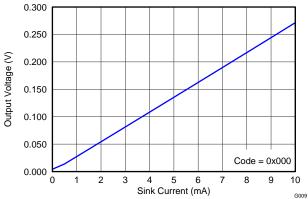

Figure 10. DAC SOURCE CURRENT

## TYPICAL CHARACTERISTICS: ADC

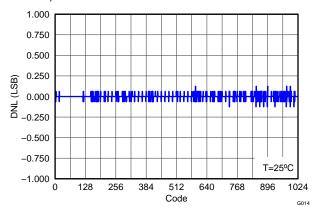

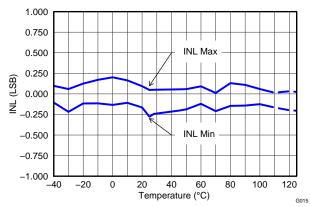

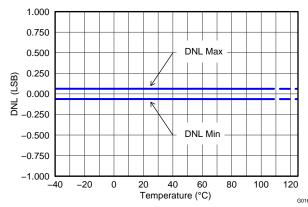

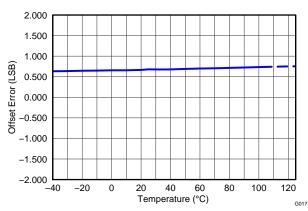

$AV_{DD} = 5 \text{ V}$ ,  $GPIOV_{DD} = 5 \text{ V}$ ,  $SPIV_{DD} = 5 \text{ V}$ , AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$  (unless otherwise noted)

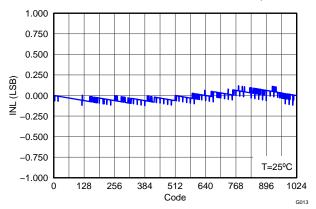

Figure 12. ADC INTEGRAL NON-LINEARITY

Figure 13. ADC DIFFERENTIAL NON-LINEARITY

Figure 14. ADC INL vs. TEMPERATURE

Figure 15. ADC DNL vs. TEMPERATURE

Figure 16. ADC OFFSET ERROR vs. TEMPERATURE

Figure 17. ADC GAIN ERROR vs. TEMPERATURE

# **TYPICAL CHARACTERISTICS: ADC (continued)**

$AV_{DD} = 5 \text{ V}$ ,  $GPIOV_{DD} = 5 \text{ V}$ ,  $SPIV_{DD} = 5 \text{ V}$ , AGND = DGND = 0 V, External ADC reference =  $AV_{DD}$

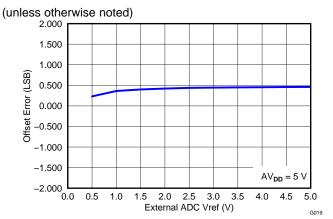

Figure 18. ADC OFFSET ERROR vs. REFERENCE VOLTAGE

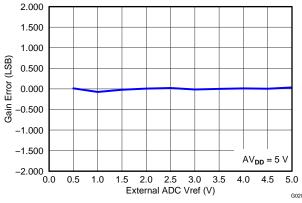

Figure 19. ADC GAIN ERROR vs. REFERENCE VOLTAGE

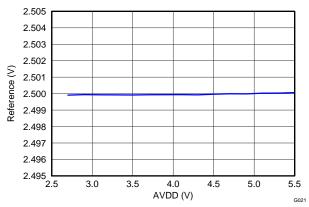

Figure 20. ADC INTERNAL REFERENCE vs. AVDD

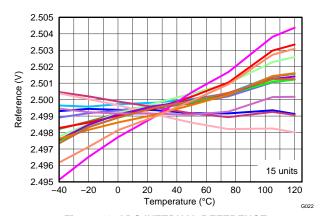

Figure 21. ADC INTERNAL REFERENCE vs. TEMPERATURE

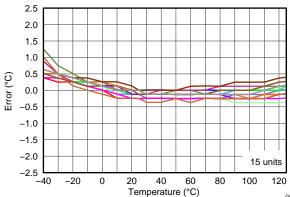

Figure 22. TEMPERATURE SENSOR ERROR vs TEMPERATURE

#### THEORY OF OPERATION

#### **SERIAL INTERFACE**

The AMC7891 is controlled through a flexible four-wire serial interface compatible with industry standard microprocessors and microcontrollers. The interface provides read/write access to all registers of the AMC7891 with clock rates up to 30 MHz.

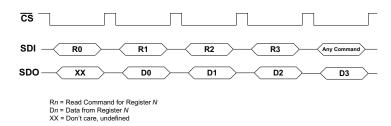

The interface is compatible with most synchronous transfer formats and is configured as a 4 pin interface. SCLK is the serial interface input clock and  $\overline{CS}$  is serial interface enable. Data is input into SDI and latched into the 24-bit wide SPI shift register on SCLK falling edges, while  $\overline{CS}$  is low. Data is clocked out of SDO on SCLK rising edges, while  $\overline{CS}$  is low. The contents of the SPI shift register are loaded into the device internal register on a  $\overline{CS}$  rising edge after some delay. When  $\overline{CS}$  is high, both SCLK and SDI inputs are blocked out and the SDO output is in high-impedance state.

The serial interface works with both a continuous and a non-continuous serial clock. A continuous SCLK source can only be used if  $\overline{CS}$  is held low for the correct number of clock cycles. In gated clock mode, a burst clock containing the exact number of clock cycles must be used and  $\overline{CS}$  must be taken high after the final clock to latch the data.

Each SPI command is input to SDI and framed by signal  $\overline{CS}$  (Serial Data Enable) asserted low. The frame's first byte into SDI is the instruction cycle which identifies the request as a read or write as well as the 7-bit address to be accessed. The following two bytes in the frame form the data cycle.

Figure 23. Serial Interface Command

- **Bit 23 R/W**. Identifies the communication as a read or write command to the addressed register. Bit = '0' sets the write operation. Bit = '1' sets the read operation.

- **Bits[22:16]** A[6:0]. Register address; specifies the register to be accessed during the read or write operation.

- **Bits[15:0] D[15:0].** Data cycle bits.

If a write command, the data cycle bits are the values to be written to the register with address A[6:0].

If a read command, the data cycle bits are don't care values.

A read command causes an output on the SDO pin during the next SPI command cycle. The SDO read value frame is formed by the previous communication instruction cycle and the data read from the specified register.

**Table 1. Serial Data Format**

| SPI FRAME        | PIN | INSTRUCTI                                                   | DATA CYLE         |                |  |  |

|------------------|-----|-------------------------------------------------------------|-------------------|----------------|--|--|

| SFI FRAIVIE      | FIN | Bit 23                                                      | Bits [22:16]      | Bits [15:0]    |  |  |

| Write Command    | SDI | 0 (R/W)                                                     | 0 (R/W) A[6:0]    |                |  |  |

| Frame            | SDO | Undefined or Read Value Frame depending on previous command |                   |                |  |  |

| Read Command     | SDI | 1 (R/W)                                                     | A[6:0]            | Don't care     |  |  |

| Frame            | SDO | Undefined or Rea                                            | nding on previous |                |  |  |

| Read Value Frame | SDI | New Write or Read Command Frame                             |                   |                |  |  |

| Read value Frame | SDO | 1 (R/W)                                                     | A[6:0]            | Data Out[15:0] |  |  |

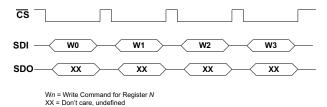

The serial clock can be continuous or gated as long as there are exactly 24 falling clock edges within the frame. A write command issued in frames whose width is not 24 bits is incorrect and ignored by the AMC7891. A read command frame not equal to 24 bits may result in abnormal data on SDO and must be ignored by the host processor. In order for another serial transfer to occur,  $\overline{CS}$  must be brought low again to start a new cycle. Figure 24 and Figure 25 show multiple write and read operations.

Figure 24. Serial Interface Write Operation

Figure 25. Serial Interface Read Operation

# **REGISTER MAP**

The AMC7891 has 16-bit registers containing device configuration and conversion results. A 7-bit register address indicates the proper register.

Table 2. Register Map

|             |      |         | MSB           |               |               |               |               |                | 0.0.          | -             |               |              |              |              |                |                |                | LSB            |

|-------------|------|---------|---------------|---------------|---------------|---------------|---------------|----------------|---------------|---------------|---------------|--------------|--------------|--------------|----------------|----------------|----------------|----------------|

|             |      |         | BIT           | BIT           | BIT           | BIT           | BIT           | BIT            | BIT           | BIT           | BIT           | BIT          | BIT          | BIT          | BIT            | BIT            | BIT            | BIT            |

| NAME        | ADDR | DEFAULT | 15            | 14            | 13            | 12            | 11            | 10             | 9             | 8             | 7             | 6            | 5            | 4            | 3              | 2              | 1              | 0              |

| TEMP_data   | 0x00 | 0x0000  | 0             | 0             | 0             | 0             |               | tempdata(11:0) |               |               |               |              |              |              |                |                |                |                |

| TEMP_config | 0x0A | 0x0008  | 0             | 0             | 0             | 0             | 0             | 0              | 0             | 0             | 0             | 0            | 0            | 0            | temp_<br>en    | 0              | 0              | 0              |

| TEMP_rate   | 0x0B | 0x0007  | 0             | 0             | 0             | 0             | 0             | 0              | 0             | 0             | 0             | 0            | 0            | 0            | 0              | te             | mp_rate(2      | 2:0)           |

| ADC0_data   | 0x23 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               | •            | adc0_c       | lata(9:0)    |                |                |                |                |

| ADC1_data   | 0x24 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | adc1_d       | lata(9:0)    |                |                |                |                |

| ADC2_data   | 0x25 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | adc2_c       | lata(9:0)    |                |                |                |                |

| ADC3_data   | 0x26 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | adc3_c       | lata(9:0)    |                |                |                |                |

| ADC4_data   | 0x27 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | adc4_c       | lata(9:0)    |                |                |                |                |

| ADC5_data   | 0x28 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | adc5_c       | lata(9:0)    |                |                |                |                |

| ADC6_data   | 0x29 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | adc6_d       | lata(9:0)    |                |                |                |                |

| ADC7_data   | 0x2A | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | adc7_c       | lata(9:0)    |                |                |                |                |

| DAC0_data   | 0x2B | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac0_c       | lata(9:0)    |                |                |                |                |

| DAC1_data   | 0x2C | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac1_c       | lata(9:0)    |                |                |                |                |

| DAC2_data   | 0x2D | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac2_c       | lata(9:0)    |                |                |                |                |

| DAC3_data   | 0x2E | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac3_c       | lata(9:0)    |                |                |                |                |

| DAC0_clear  | 0x2F | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac0_c       | lear(9:0)    |                |                |                |                |

| DAC1_clear  | 0x30 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac1_c       | lear(9:0)    |                |                |                |                |

| DAC2_clear  | 0x31 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac2_c       | lear(9:0)    |                |                |                |                |

| DAC3_clear  | 0x32 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              |               |               |               |              | dac3_c       | lear(9:0)    |                |                |                |                |

| GPIO_config | 0x33 | 0x0000  | 0             | 0             | 0             | 0             | ioc3_<br>io   | ioc2_<br>io    | ioc1_<br>io   | ioc0_<br>io   | iob3_<br>io   | iob2_<br>io  | iob1_<br>io  | iob0_<br>io  | ioa3_<br>io    | ioa2_<br>io    | ioa1_<br>io    | ioa0_<br>io    |

| GPIO_out    | 0x34 | 0x0000  | 0             | 0             | 0             | 0             | ioc3_<br>out  | ioc2_<br>out   | ioc1_<br>out  | ioc0_<br>out  | iob3_<br>out  | iob2_<br>out | iob1_<br>out | iob0_<br>out | ioa3_<br>out   | ioa2_<br>out   | ioa1_<br>out   | ioa0_<br>out   |

| GPIO_in     | 0x35 | NA      | 0             | 0             | 0             | 0             | ioc3_<br>in   | ioc2_<br>in    | ioc1_<br>in   | ioc0_<br>in   | iob3_<br>in   | iob2_<br>in  | iob1_<br>in  | iob0_<br>in  | ioa3_<br>in    | ioa2_<br>in    | ioa1_<br>in    | ioa0_<br>in    |

| AMC_config  | 0x36 | 0x2000  | 0             | 0             | adc_<br>mode  | adc_tr<br>ig  | dac_lo<br>ad  | resvd          | adc_ra        | ate(1:0)      | adc_r<br>eady | 0            | 0            | 0            | 0              | 0              | 0              | 0              |

| ADC_enable  | 0x37 | 0x0000  | 0             | adc0_<br>en   | adc1_<br>en   | resvd         | adc2_<br>en   | adc3_<br>en    | resvd         | adc4_<br>en   | adc5_<br>en   | adc6_<br>en  | adc7_<br>en  | 0            | 0              | 0              | 0              | 0              |

| ADC_gain    | 0x38 | 0xFF00  | adc0_<br>gain | adc1_<br>gain | adc2_<br>gain | adc3_<br>gain | adc4_<br>gain | adc5_<br>gain  | adc6_<br>gain | adc7_<br>gain | 0             | 0            | 0            | 0            | 0              | 0              | 0              | 0              |

| DAC_clear   | 0x39 | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              | 0             | 0             | 0             | 0            | 0            | 0            | dac3_<br>clear | dac2_<br>clear | dac1_<br>clear | dac0_<br>clear |

| DAC_sync    | 0x3A | 0x0000  | 0             | 0             | 0             | 0             | 0             | 0              | 0             | 0             | 0             | 0            | 0            | 0            | dac3_<br>sync  | dac2_<br>sync  | dac1_<br>sync  | dac0_<br>sync  |

| AMC_power   | 0x3B | 0x0000  | 0             | adc_o<br>n    | ref_on        | dac0_<br>on   | dac1_<br>on   | dac2_<br>on    | dac3_<br>on   | 0             | 0             | 0            | 0            | 0            | 0              | 0              | 0              | 0              |

| AMC_reset   | 0x3E | 0x0000  |               |               |               |               |               |                |               | reset         | (15:0)        |              |              |              |                |                |                |                |

| AMC_ID      | 0x40 | 0x0044  |               |               |               |               |               |                |               | device        | _id(15:0)     |              |              |              |                |                |                |                |

## **REGISTER DESCRIPTIONS**

Register name: temp\_data - Address: 0x00, Default: 0x0000 (READ ONLY)

| . tog.oto        |         |       | . ccc. cato, zc.aa | 0.0000 ()                                                                     |               |

|------------------|---------|-------|--------------------|-------------------------------------------------------------------------------|---------------|

| Register<br>Name | Address | Bit   | Name               | Function                                                                      | Default Value |

| temp_data        | 0x00    | 15:12 | Reserved           | Reserved for factory use.                                                     | All zeros     |

|                  |         | 11:0  | temp_data(11:0)    | Stores the temperature sensor reading in twos complement format. 0.125°C/LSB. | 0x000         |

Register name: temp\_config - Address: 0x0A, Default: 0x0008 (READ/WRITE)

| •                | . –     | •    | ,        | ,                                                           |               |

|------------------|---------|------|----------|-------------------------------------------------------------|---------------|

| Register<br>Name | Address | Bit  | Name     | Function                                                    | Default Value |

| temp_config      | 0x0A    | 15:4 | Reserved | Reserved for factory use.                                   | All zeros     |

|                  |         | 3    | temp_en  | When set to '1', the on-chip temperature sensor is enabled. | 1             |

|                  |         | 2:0  | Reserved | Reserved for factory use.                                   | All zeros     |

Register name: temp\_rate - Address: 0x0B, Default: 0x0007 (READ/WRITE)

| Register<br>Name | Address | Bit  | Name           |      | F                                               | unction         | Default Val |  |

|------------------|---------|------|----------------|------|-------------------------------------------------|-----------------|-------------|--|

| temp_rate        | 0x0B    | 15:3 | Reserved       | Res  | erved for factory use.                          |                 | All zeros   |  |

| 2                |         | 2:0  | temp_rate(2:0) | Sets | Sets the temperature sensor ADC conversion time |                 |             |  |

|                  |         |      |                |      | temp_rate(2:0)                                  | Conversion time |             |  |

|                  |         |      |                |      | 000                                             | 128x            |             |  |

|                  |         |      |                |      | 001                                             | 64x             |             |  |

|                  |         |      |                |      | 010                                             | 32x             |             |  |

|                  |         |      |                |      | 011                                             | 16x             |             |  |

|                  |         |      |                |      | 100                                             | 8x              |             |  |

|                  |         |      |                |      | 101                                             | 4x              |             |  |

|                  |         |      |                |      | 110                                             | 2x              |             |  |

|                  |         |      |                |      | 111                                             | 15 ms           |             |  |

Register name: ADCn\_data - Address: 0x23 to 0x2A, Default: 0x0000 (READ ONLY)(1)

| Register<br>Name | Address | Bit                 | Name           |                | Default Value         |                               |                   |           |

|------------------|---------|---------------------|----------------|----------------|-----------------------|-------------------------------|-------------------|-----------|

| ADCn_            | 0x23 to | 15:10               | Reserved       | Rese           | erved for factory use |                               |                   | All zeros |

| data 0x2A        | 0x2A    | 9:0                 | adcn_data(9:0) | Store          | es the 10-bit ADCn o  | conversion results in straigh | nt binary format. | All zeros |

|                  |         |                     |                | Input Channel  | ADC Register Value    | Register<br>Address           |                   |           |

|                  |         |                     |                |                | AIN_0                 | adc0_data(9:0)                | 0x23              |           |

|                  |         |                     |                |                | AIN_1                 | adc1_data(9:0)                | 0x24              |           |

|                  |         |                     |                |                | AIN_2                 | adc2_data(9:0)                | 0x25              |           |

|                  |         |                     |                |                | AIN_3                 | adc3_data(9:0)                | 0x26              |           |

|                  |         |                     |                |                | AIN_4                 | adc4_data(9:0)                | 0x27              |           |

|                  |         | AIN_6 adc6_data(9:0 | adc5_data(9:0) | 0x28           |                       |                               |                   |           |

|                  |         |                     | AIN_6          | adc6_data(9:0) | 0x29                  |                               |                   |           |

|                  |         |                     |                |                | AIN_7                 | adc7_data(9:0)                | 0x2A              |           |

(1) All ADCn\_data registers are formatted in the manner shown here. n = 0, 1, ..., 7

Register name: DACn\_data - Address: 0x2B to 0x2E, Default: 0x0000 (READ/WRITE)(1)

| Register<br>Name | Addres<br>s | Bit   | Name                        |    |                                                                                            | Function              |                     | Default<br>Value |  |

|------------------|-------------|-------|-----------------------------|----|--------------------------------------------------------------------------------------------|-----------------------|---------------------|------------------|--|

| DACn_ data       | 0x2B to     | 15:10 | Reserved                    | Re | Reserved for factory use.                                                                  |                       |                     |                  |  |

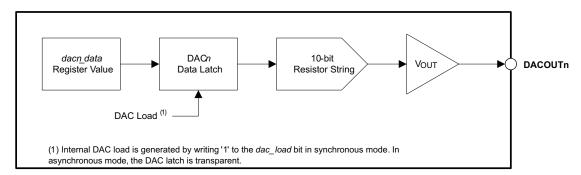

| 0x2E             | 0x2E        | 9:0   | 9:0 dac <i>n</i> _data(9:0) |    | Stores the 10-bit data to be loaded to the DAC <i>n</i> latches in straight binary format. |                       |                     |                  |  |